# Keysight N4962A Serial BERT 12.5 Gb/s

Data Sheet

#### **Features**

- Internal and external clock system

- 0.5 to 12.5 Gb/s operation

- Multiple clock and pattern triggers

- Differential or single-ended input and outputs

- Programmable output amplitude control

- Selectable PRBS pattern length, mark-space density

- Local push-button and GPIB remote interface

The Keysight Technologies, Inc. N4962A serial BERT 12.5 Gb/s is a small size, high-performance 0.5 to 12.5 Gb/s pseudo-random bit sequence generator and bit error rate tester designed for automated production-line testing, manufacturing and R&D lab use.

This GPIB controllable BERT, with its small size, is ideal for mounting close to the device under test and minimizes cabling. The internal synthesizer offers performance from 9.90 to 11.35 Gb/s. When used in conjunction with an external clock (e.g., N4963A), operation from 0.5 to 12.5 Gb/s is possible. The BERT offers 5 PRBS patterns for stressing different types of data networks. In addition, the jitter injection capabilities allows frequency modulation with DC-100 MHz bandwidth, for inducing a stressed eye for receiver measurements.

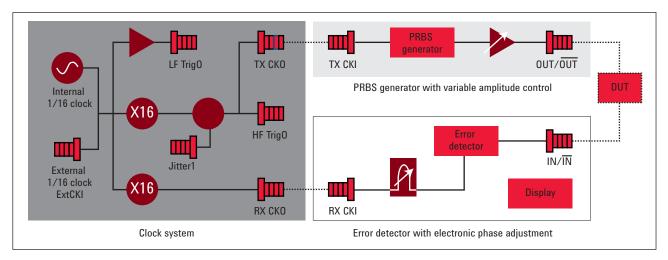

# Block diagram

Figure 1. Block diagram

# Clock system specifications

|                                                           | Specification                                                                                          |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| TXCKO, RXCKO high frequency clock output                  | 9.90 to 11.35 GHz , (overprogrammable to 9.85 GHz) <sup>1</sup>                                        |

| TXCKO, RXCKO output amplitude                             | 1 Vpp typical                                                                                          |

| TXCKO, RXCKO external interface                           | AC coupled female SMA 50 $\Omega$                                                                      |

| Frequency resolution                                      | MHz when GPIB controlled MHz when front panel controlled                                               |

| HF TrigO frequency range                                  | 9.90 to 11.35 GHz                                                                                      |

| HF TrigO output amplitude                                 | 1.3 Vpp typical                                                                                        |

| HF TrigO external interface                               | AC coupled female SMA 50 $\Omega$                                                                      |

| LF TrigO frequency range (1/16)                           | 618.75 to 709.375 MHz                                                                                  |

| LF TrigO output amplitude                                 | 0.5 Vpp typical                                                                                        |

| LF TrigO external interface                               | AC coupled female SMA 50 Ω                                                                             |

| ExtCKI external 1/16 clock input frequency range          | 618.75 to 709.375 MHz <sup>2</sup>                                                                     |

| ExtCKI input amplitude                                    | 2 V pp max                                                                                             |

| ExtCKI external interface                                 | AC coupled female SMA 50 Ω                                                                             |

| Jitterl external jitter input frequency range             | DC to 100 MHz                                                                                          |

| Jitterl external jitter input voltage                     | 2 Vpp max                                                                                              |

| Jitterl external Interface                                | DC coupled female SMA 50 $\Omega$                                                                      |

| Jitter amplitude (applied to TXCKO and HF TrigO outpu;ts) | Up to 5 UI at modulation frequencies of ≤ 2 MHz<br>Up to 0.15 UI at modulation frequencies of ≥ 10 MHz |

Internal clock is over-programmble down to 9.85 GHz, but performance below 9.90 GHz is not guaranteed

Operation with external 1/16 clock down to 615.625 MHz is possible but operation below 618.75 MHz is not guaranteed

|                                         | Units                                                                                                                                         |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| PRBS generator                          |                                                                                                                                               |

| Data rate                               | 0.5 to 12.5 Gb/s                                                                                                                              |

| PRBS patterns                           | 2n – 1, n=7, 10, 15, 23, 31                                                                                                                   |

| Mark space density                      | 1/2, 1/4, 1/8                                                                                                                                 |

| Pattern invert                          | available for all patterns                                                                                                                    |

| Error injection                         | selectable uniform rate                                                                                                                       |

| Error injection rates                   | 1 x10n errors per second, n = 1, 2, 3, 4, 5, 6, 7                                                                                             |

| Data output amplitude                   | 300 to 1800 mVpp (single-ended)                                                                                                               |

| Data output amplitude resolution        | 10 mV                                                                                                                                         |

| Data output jitter                      | 1.1 ps rms typical at 10 Gb/s                                                                                                                 |

| Data output rise/fall time (20% to 80%) | 18 ps typical, 23 ps maximum                                                                                                                  |

| Data output external interface          | Differential; AC coupled, 50 $\Omega$ nominal, female 2.92 mm (May be operated single end without unused output terminated into 50 $\Omega$ ) |

| TXCKI clock input frequency range       | 0.5 to 12.5 GHz                                                                                                                               |

| TXCKI clock input amplitude range       | 0 to +5 dBm (630 mVpp to 1.1 Vpp)                                                                                                             |

| TXCKI clock input external interface    | AC coupled, 50 $\Omega$ nominal, female SMA                                                                                                   |

| Error detector                          |                                                                                                                                               |

| Data rate                               | 0.5 to 12.5 Gb/s                                                                                                                              |

| PRBS patterns                           | 2n-1, n = 7, 10, 15, 23, 31                                                                                                                   |

| Data input sensitivity (single ended)   | 0.1 Vpp typical                                                                                                                               |

| Data input voltage range                | 2 Vpp max (single-ended)<br>±0.5 V DC common mode voltage max                                                                                 |

| Data input phase adjust                 | 0 to 360°                                                                                                                                     |

| Data input phase adjust resolution      | 2° for data rates ≥ 5 Gb/s<br>90° for data rates < 5 Gb/s                                                                                     |

| Data input external interface           | Differential; DC coupled, 50 $\Omega$ nominal, female SMA (May be operated single end without unused input terminated into 50 $\Omega$ )      |

| RXCKI clock input frequency range       | 0.5 to 12.5 GHz                                                                                                                               |

| RXCKI clock input amplitude range       | 0 to +5 dBm (630 mVpp to 1.1 Vpp)                                                                                                             |

| RXCKI clock input external interface    | AC coupled, 50 Ω nominal, female SMA                                                                                                          |

|                                                  | Description                                                            |

|--------------------------------------------------|------------------------------------------------------------------------|

| General and mechanical parameters                |                                                                        |

| Operating temperature                            | +10 °C to +40 °C                                                       |

| Storage temperature                              | -40 °C to +70 °C                                                       |

| Power requirements                               | 42 W external AC adaptor (included)                                    |

|                                                  | 100 to 240 V AC, 47 to 63 Hz                                           |

| Physical dimensions                              | Width: 254 mm (10 in), height: 63.5 mm (2.5 in), depth: 254 mm (10 in) |

| Weight                                           | 3.4 kg (7.5 lbs)                                                       |

| Regulatory standards                             |                                                                        |

| EMC                                              |                                                                        |

| Complies with European EMC Directive 2004/108/EC | IEC/EN 61326-1                                                         |

|                                                  | CISPR Pub 11 Group 1, class A                                          |

|                                                  | AS/NZS CISPR 11                                                        |

|                                                  | ICES/NMB-001                                                           |

|                                                  | This ISM device complies with Canadian                                 |

|                                                  | ICES-001                                                               |

|                                                  | This ISM device complies with Canadian ICES-001                        |

|                                                  | Cet appareil ISM est conforme a la norme NMB-001 du Canada.            |

### Ordering information

All accessories required for operation are shipped with the system including those listed in the accessory table below and do not need to be purchased separately.

| N4962A Accessories |     |                                 |  |

|--------------------|-----|---------------------------------|--|

| Part number        | Qty | Description                     |  |

| 11571-006          | 1   | Power adapter                   |  |

| 12310-023          | 1   | Cable pair, data loop-back      |  |

| 12310-024          | 1   | Cable, clock loop-back, outside |  |

| 12310-025          | 1   | Cable, clock loop-back, inside  |  |

| N4960-60026        | 2   | Cable, 2.92 mm M-F, 5.5 in      |  |

| N8990-01910        | 4   | Adapter, 2.92 mm M-2.92 mm F    |  |

N4962A serial BERT 12.5 Gb/s: 0.5 to 12.5 Gb/s PRBS pattern generator and error detector system with internal 9.90 to 11.35 GHz clock system.

For operation outside the range of 9.9 to 11.35 Gb/s an external clock source is required. Recommended model is N4963A Clock Synthesizer 13.5 GHz

#### Calibration service

For calibration service information, contact your local authorized Keysight distributor or Keysight sales department.

### Ordering contact

For additional information, to schedule a demo, or to request a quote, please contact your local authorized Keysight distributor or Keysight sales department.